Today’s computer systems, with their emphasis on high resolution graphics, full motion video, high bandwidth networking, and so on, go far beyond the capabilities of the architecture that ushered in the age of the personal computer in 1982. Modern PC systems demand high performance interconnects that also allow devices to be changed or upgraded with a minimum of effort by the end user.

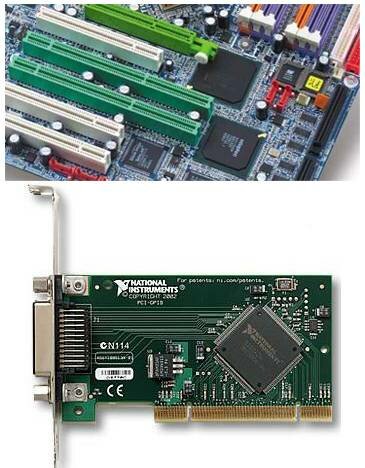

In response to this need, PCI (peripheral component interconnect) has emerged as the dominant mechanism for interconnecting the elements of modern, high performance computer systems. It is a well thought out standard with a number of forward looking features that should keep it relevant well into the next century. Originally conceived as a mechanism for interconnecting peripheral components on a motherboard, PCI has evolved into at least a half dozen different physical implementations directed at specific market segments yet all using the same basic bus protocol. In the form known as Compact PCI, it is having a major impact in the rapidly growing telecommunications market.

PCI offers a number of significant performance and architectural advantages over previous busses:

Speed:The basic PCI protocol can transfer up to 132 Mbytes per second, well over an order of magnitude faster than ISA. Even so, the demand for bandwidth is insatiable. Extensions to the basic protocol yield bandwidths as high as 512 Mbytes per second and development currently under way will push it to a gigabyte.

Configurability:PCI offers the ability to configure a system automatically, relieving the user of the task of system configuration. It could be argued that PCI’s success owes much to the very fact that users need not be aware of it.

Multiple Masters:Prior to PCI, most busses supported only one “master,” the processor. High bandwidth devices could have direct access to memory through a mechanism called DMA (direct memory access) but devices, in general, could not talk to each other. In PCI, any device has the potential to take control of the bus and initiate transactions with any other device.

Reliability:“Hot Plug” and “Hot Swap,” defined respectively for PCI and Compact PCI, offer the ability to replace modules without disrupting a system’s operation. This substantially reduces MTTR (mean time to repair) to yield the necessary degree of up-time required of mission-critical systems such as the telephone network.

1. PCI Protocol

PCI is a synchronous bus architecture with all data transfers being performed relative to a system clock (CLK). The initial PCI specification permitted a maximum clock rate of 33 MHz allowing one bus transfer to be performed every 30 nanoseconds. Later, PCI specification extended the bus definition to support operation at 66 MHz, but the vast majority of today’s personal computers continue to implement a PCI bus that runs at a maximum speed of 33 MHz.

PCI implements a 32-bit multiplexed Address and Data bus (AD[31:0]). It architects a means of supporting a 64-bit data bus through a longer connector slot, but most of today’s personal computers support only 32-bit data transfers through the base 32-bit PCI connector. At 33 MHz, a 32-bit slot supports a maximum data transfer rate of 132 MBytes/sec, and a 64-bit slot supports 264 MBytes/sec.

The multiplexed Address and Data bus allows a reduced pin count on the PCI connector that enables lower cost and smaller package size for PCI components. Typical 32-bit PCI add-in boards use only about 50 signals pins on the PCI connector of which 32 are the multiplexed Address and Data bus. PCI bus cycles are initiated by driving an address onto the AD[31:0] signals during the first clock edge called the address phase. The address phase is signaled by the activation of the FRAME# signal. The next clock edge begins the first of one or more data phases in which data is transferred over the AD[31:0] signals.

In PCI terminology, data is transferred between an initiator which is the bus master, and a target which is the bus slave. The initiator drives the C/BE[3:0]# signals during the address phase to signal the type of transfer (memory read, memory write, I/O read, I/O write, etc.). During data phases the C/BE[3:0]# signals serve as byte enable to indicate which data bytes are valid. Both the initiator and target may insert wait states into the data transfer by deasserting the IRDY# and TRDY# signals. Valid data transfers occur on each clock edge in which both IRDY# and TRDY# are asserted.

A PCI bus transfer consists of one address phase and any number of data phases. I/O operations that access registers within PCI targets typically have only a single data phase. Memory transfers that move blocks of data consist of multiple data phases that read or write multiple consecutive memory locations. Both the initiator and target may terminate a bus transfer sequence at any time. The initiator signals completion of the bus transfer by deasserting the FRAME# signal during the last data phase. A target may terminate a bus transfer by asserting the STOP# signal. When the initiator detects an active STOP# signal, it must terminate the current bus transfer and re-arbitrate for the bus before continuing. If STOP# is asserted without any data phases completing, the target has issued a retry. If STOP# is asserted after one or more data phases have successfully completed, the target has issued a disconnect.

Initiators arbitrate for ownership of the bus by asserting a REQ# signal to a central arbiter. The arbiter grants ownership of the bus by asserting the GNT# signal. REQ# and GNT# are unique on a per slot basis allowing the arbiter to implement a bus fairness algorithm. Arbitration in PCI is “hidden” in the sense that it does not consume clock cycles. The current initiator’s bus transfers are overlapped with the arbitration process that determines the next owner of the bus.

PCI supports a rigorous auto configuration mechanism. Each PCI device includes a set of configuration registers that allow identification of the type of device (SCSI, video, Ethernet, etc.) and the company that produced it. Other registers allow configuration of the device’s I/O addresses, memory addresses, interrupt levels, etc.

Although it is not widely implemented, PCI supports 64-bit addressing. Unlike the 64-bit data bus option which requires a longer connector with additional 32-bits of data signals, 64-bit addressing can be supported through the base 32-bit connector. Dual Address Cycles are issued in which the low order 32-bits of the address are driven onto the AD[31:0] signals during the first address phase, and the high order 32-bits of the address (if non-zero) are driven onto the AD[31:0] signals during a second address phase. The remainder of the transfer continues like a normal bus transfer.

PCI defines support for both 5 Volt and 3.3 Volt signaling levels. The PCI connector defines pin locations for both the 5 Volt and 3.3 Volt levels. However, most early PCI systems were 5 Volt only, and did not provide active power on the 3.3 Volt connector pins. Over time more use of the 3.3 Volt interface is expected, but add-in boards which must work in older legacy systems are restricted to using only the 5 Volt supply. A “keying” scheme is implemented in the PCI connectors to prevent inserting an add-in board into a system with incompatible supply voltage.

Although used most extensively in PC compatible systems, the PCI bus architecture is processor independent. PCI signal definitions are generic allowing the bus to be used in systems based on other processor families. PCI includes strict specifications to ensure the signal quality required for operation at 33 and 66 MHz. Components and add-in boards must include unique bus drivers that are specifically designed for use in a PCI bus environment. Typical TTL devices used in previous bus implementations such as ISA and EISA are not compliant with the requirements of PCI. This restriction along with the high bus speed dictates that most PCI devices are implemented as custom ASICs.

The higher speed of PCI limits the number of expansion slots on a single bus to no more than 3 or 4, as compared to 6 or 7 for earlier bus architectures. To permit expansion buses with more than 3 or 4 slots, the PCI SIG has defined a PCI-to-PCI Bridge mechanism. PCI-to-PCI Bridges are ASICs that electrically isolate two PCI buses while allowing bus transfers to be forwarded from one bus to another. Each bridge device has a “primary” PCI bus and a “secondary” PCI bus. Multiple bridge devices may be cascaded to create a system with many PCI buses.

Chapters:

- Introduction to PCI protocol

- PCI Signal Descriptions

- PCI Bus Transactions

- PCI Bus Timing Diagrams

- Configuration space decoding

- Arbitration process under PCI

- Error Detection and Reporting

Bibliography

- PCI Tutorial by Xilinx

- PCI Bus Demystified by Doug Abbott

Submitted by: Rovin and Sagar

i cannot access anything but the first page

Hi,

Nice post, but you may want to fix Chapter 5: Configuration space decoding.

“CONFIG_ADDRESS 0x3f8

CONFIG_DATA 0x3fc”

0x3F8 and 0x3FC are UART0, not the PCI registers. Note that the diagram shows the correct address.

I understand PCI finally….Thanks….

I would know the différence between the PCI prtocol and VME protocol.

if it is possible! thanks

Historians have found references to early forms of baseball from the 1820’s and 1830’s in New York City state, Philadelphia,

Massachusetts, New Hampshire, Vermont, and other northeastern states.

8 years ago, Jung Da-Yeon was a homely, out-of-shape Korean woman. 19

But Mary kept all these things and pondered them in her heart.