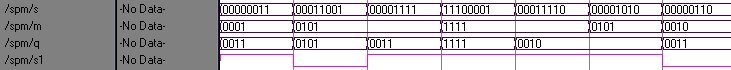

Verilog HDL Program for Serial Parallel Multiplier.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 | module spm(s,m,q); output [7:0]s; input [3:0]m,q; and1 u1(s[0],m[0],q[0]); and1 u2(s1,m[0],q[1]); and1 u3(s2,m[0],q[2]); and1 u4(s3,m[0],q[3]); and1 u5(s4,m[1],q[0]); and1 u6(s5,m[1],q[1]); and1 u7(s6,m[1],q[2]); and1 u8(s7,m[1],q[3]); and1 u9(s8,m[2],q[0]); and1 u10(s9,m[2],q[1]); and1 u11(s10,m[2],q[2]); and1 u12(s11,m[2],q[3]); and1 u13(s12,m[3],q[0]); and1 u14(s13,m[3],q[1]); and1 u15(s14,m[3],q[2]); and1 u16(s15,m[3],q[3]); parad4 u21({s18,s17,s16,s[1]},c3,{s7,s6,s5,s4},{1'b0,s3,s2,s1}); parad4 u22({s21,s20,s19,s[2]},c7,{c3,s18,s17,s16},{s11,s10,s9,s8}); parad4 u23({s[6],s[5],s[4],s[3]},s[7],{c7,s21,s20,s19},{s15,s14,s13,s12}); endmodule module parad4(a,c,p,q); // Parallel Adder Module output [3:0]a; output c; input [3:0]p,q; wire c1,c2,c3; ha u1(a[0],c1,p[0],q[0]); fa u2(a[1],c2,p[1],q[1],c1); fa u3(a[2],c3,p[2],q[2],c2); fa u4(a[3],c,p[3],q[3],c3); endmodule |