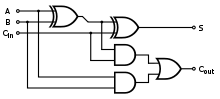

A full adder adds binary numbers and accounts for values carried in as well as out. A one-bit full adder adds three one-bit numbers, often written as A, B, and Cin; A and B are the operands, and Cin is a bit carried in from the next less significant stage. The full-adder is usually a component in a cascade of adders, which add 8, 16, 32, etc. binary numbers. The circuit produces a two-bit output sum typically represented by the signals Cout and S, where sum = 2XCout + S.

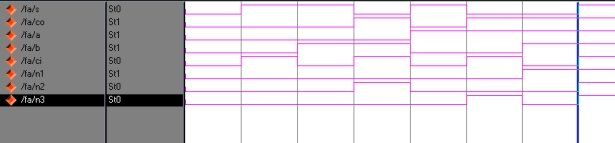

1 2 3 4 5 6 7 8 9 | module fa(s,co,a,b,ci); output s,co; input a,b,ci; xor1 u1(s,a,b,ci); and1 u2(n1,a,b); and1 u3(n2,b,ci); and1 u4(n3,a,ci); or1 u5(co,n1,n2,n3); endmodule |

good.

I want to get verilog hdl code for 8-bit carry save array multiplier.Can you help in getting it to me?