The Negated AND, NOT AND or NAND gate is the opposite of the digital AND gate, and behaves in a manner that corresponds to the opposite of AND gate. A LOW (0) output results only if both the inputs to the gate are HIGH (1); if one or both inputs are LOW (0), a HIGH (1) output results.

The NAND gate is significant because any boolean function can be implemented by using a combination of NAND gates. This property is called functional completeness.

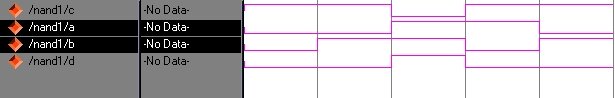

1 2 3 4 5 6 7 | module nand1(c,a,b); output c; input a,b; wire d; and1 u1(d,a,b); inv u2(c,d); endmodule |