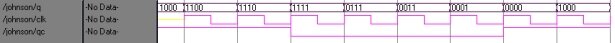

Verilog HDL Program for Johnson Counter.

1 2 3 4 5 6 7 8 9 | module johnson(q,clk); output [3:0]q; input clk; not (qc,q[0]); dff u1(q[3],qc,clk); dff1 u2(q[2],q[3],clk); dff1 u3(q[1],q[2],clk); dff1 u4(q[0],q[1],clk); endmodule |

Verilog HDL Program for Johnson Counter.

1 2 3 4 5 6 7 8 9 | module johnson(q,clk); output [3:0]q; input clk; not (qc,q[0]); dff u1(q[3],qc,clk); dff1 u2(q[2],q[3],clk); dff1 u3(q[1],q[2],clk); dff1 u4(q[0],q[1],clk); endmodule |

Be the first to receive the latest updates from Codesdoc by signing up to our email subscription.