A flip-flop or latch is a circuit that has two stable states and can be used to store state information. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.

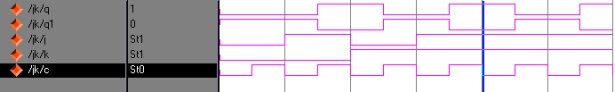

The JK flip-flop augments the behavior of the SR flip-flop (J=Set, K=Reset) by interpreting the S = R = 1 condition as a “flip” or toggle command. Specifically, the combination J = 1, K = 0 is a command to set the flip-flop; the combination J = 0, K = 1 is a command to reset the flip-flop; and the combination J = K = 1 is a command to toggle the flip-flop.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 | module jk(q,q1,j,k,c); output q,q1; input j,k,c; reg q,q1; initial begin q=1'b0; q1=1'b1; end always @ (posedge c) begin case({j,k}) {1'b0,1'b0}:begin q=q; q1=q1; end {1'b0,1'b1}: begin q=1'b0; q1=1'b1; end {1'b1,1'b0}:begin q=1'b1; q1=1'b0; end {1'b1,1'b1}: begin q=~q; q1=~q1; end endcase end endmodule |

Thanks a lot. NIce work

nice thank u…

I do not see many comments here, it means you have not many visitors. I know how to make your website go viral. If you want to know simply search in google for:

Kimting’s Method To Go Viral