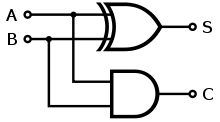

The half adder adds two one-bit binary numbers A and B. It has two outputs, S and C (the value theoretically carried on to the next addition); the final sum is 2C + S. The simplest half-adder design, pictured on below, incorporates an XOR gate for S and an AND gate for C. With the addition of an OR gate to combine their carry outputs, two half adders can be combined to make a full adder.

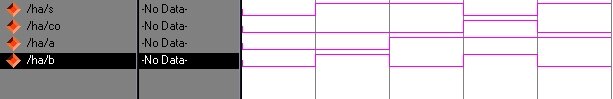

1 2 3 4 5 6 | module ha(s,co,a,b); output s,co; input a,b; xor1 u1(s,a,b); and1 u2 (co,a,b); endmodule |