The XOR gate is a digital logic gate that implements an exclusive or; that is, a true output (1) results if one, and only one, of the inputs to the gate is true (1). If both inputs are false (0) or both are true (1), a false output (0) results. A way to remember XOR is “one or the other but not both”. It represents the inequality function, i.e., the output is HIGH (1) if the inputs are not alike otherwise the output is LOW (0).

This Function is addition modulo 2. As a result, XOR gates are used to implement binary addition in computers. A half adder consists of an XOR gate and an AND gate.

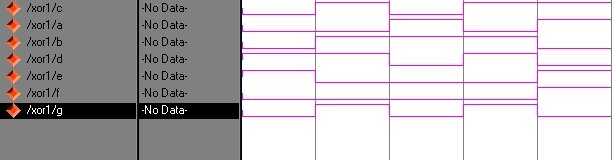

1 2 3 4 5 6 7 8 9 10 | module xor1(c,a,b); output c; input a,b; wire d,e,f,g; inv u1(d,a); inv u2(e,b); and1 u3(f,a,e); and1 u4(g,b,d); or1 u5(c,f,g); endmodule |