A 4 bit binary parallel adder can be formed by cascading four full adder units. The carry of each stage is connected to the next unit as the carry in (That is the third input).

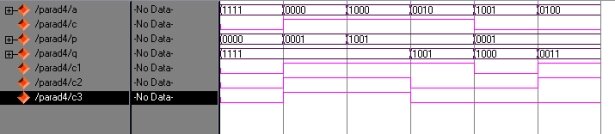

1 2 3 4 5 6 7 8 9 10 | module parad4(a,c,p,q); output [3:0]a; output c; input [3:0]p,q; wire c1,c2,c3; ha u1(a[0],c1,p[0],q[0]); fa u2(a[1],c2,p[1],q[1],c1); fa u3(a[2],c3,p[2],q[2],c2); fa u4(a[3],c,p[3],q[3],c3); endmodule |

i want combined vlsi notes