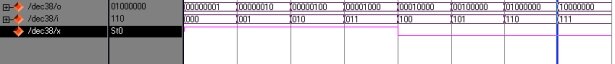

A decoder is a device which does the reverse operation of an encoder, undoing the encoding so that the original information can be retrieved. The same method used to encode is usually just reversed in order to decode. It is a combinational circuit that converts binary information from n input lines to a maximum of 2n unique output lines.

1 2 3 4 5 6 7 8 | module dec38(o,i); output [7:0]o; input [2:0]i; wire x; inv u1(x,i[2]); decoder24 u2(o[3:0],i[1],i[0],x); decoder24 u3(o[7:4],i[1],i[0],i[2]); endmodule |

I like this post, enjoyed this one thankyou for putting up. Jones sabo i really do the actual http://whymyface.com/members/home

Whether you’re a business or personal brand, you should definitely

pay attention to Pinterest. Unfortunately, it’s also introduced a host of ways to violate

intellectual property laws. The more powerful the

image, the more interest you will provoke in visitors to your profile which in turn will result

in your profile attracting more followers.