A decoder is a device which does the reverse operation of an encoder, undoing the encoding so that the original information can be retrieved. The same method used to encode is usually just reversed in order to decode. It is a combinational circuit that converts binary information from n input lines to a maximum of 2n unique output lines.

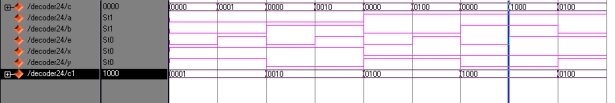

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 | module decoder24(c,a,b,e); output [3:0]c; input a,b,e; wire x,y; wire [3:0]c1; inv u1(x,a); inv u2(y,b); and1 u3(c1[0],x,y); and1 u4(c1[1],x,b); and1 u5(c1[2],a,y); and1 u6(c1[3],a,b); and1 u7(c[0],c1[0],e); and1 u8(c[1],c1[1],e); and1 u9(c[2],c1[2],e); and1 u10(c[3],c1[3],e); endmodule |

ghgfhgggggggggggggggggfetg